新启辰教育

123.06M · 2026-03-05

近日,有个大佬通过挖掘 Apple Neural Engine (ANE) ,针对苹果芯片底层 AI 逻辑做了一次细节公开,因为苹果 ANE(M4 芯片上为 16 核运算单元)长期以来是一个纯粹的“黑盒”,对大家来说缺少公开接口、文档和指令集架构 (ISA),开发者只能通过 CoreML 框架间接调用,而这次作者 maderix 通过挖掘把 CoreML 给大家理清了一个清晰的轮廓。

首先,maderix 是通过一些常用手段来获取数据:

dyld_info 扫描私有 framework,通过 Method Swizzling hook CoreML (MIL)也就是实现了内存中将 MIL 直接编译为 ANE binary ,这可以让开发者绕过苹果的官方限制,直接在 ANE 上进行神经网络的训练和推理调用。

而在直接测试硬件底层的过程中,maderix 发现了几个关于 ANE 的结论:

是不是觉得有点懵逼,其实很好理解,通俗的讲:

而苹果的 ANE 在处理 INT8 “图纸”时,并没有直接用“看缩略图”的快速方式,而是偷偷地把这张“缩略图”又还原(反量化)成“高清图纸”(FP16) ,然后再拿去处理,这就像是明明有一台能快速扫描缩略图的机器,苹果却非要先把缩略图放大成高清图,再用处理高清图的慢速机器去扫描。

ml-ane-transformers 参考代码中曾有隐晦的暗示,里面大量用卷积模拟 Transformer 结构)这就像一家专门做跑车发动机的工厂,你非要它去生产家用轿车的变速箱,它的效率就会变得低下,而「1x1 Conv 走卷积 datapath,MatMul 走 fallback 路径」可以理解为工厂内部有两条完全不同的“生产线” :

这个就更好理解,ANE 在这里不是“16个独立工人”,而是一条“16道工序的自动化流水线”,它的16个核心不是独立的,而是像接力赛一样串起来的,每个核心负责AI计算中的一个特定阶段。

这计算图就是交给那条16道工序流水线的一份详细的、总装的“流程图” ,这样在完整的全貌流程图下,流水线的总调度才能完整工作起来。

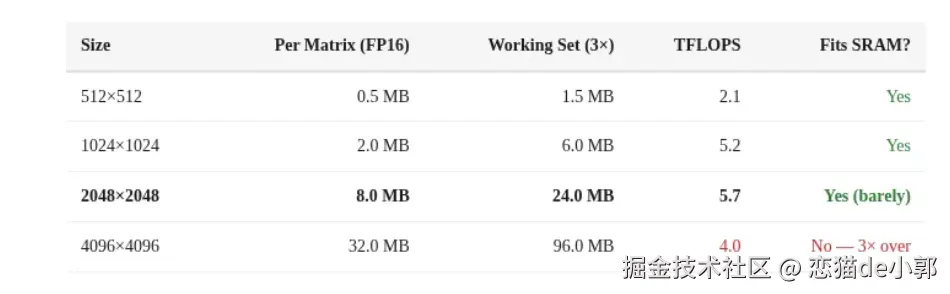

| 官方 | 推测 | |

|---|---|---|

| INT8 | 38 TOPS | ≈ 19 TFLOPS 等效 |

| FP16 | 未强调 | ≈ 19 TFLOPS |

| SRAM | 未公开 | ≈ 32MB |

| 单算子利用率 | 未说明 | ≈ 30% |

| 图级利用率 | 未说明 | ≈ 94% |

最后,作者得到一个结论:ANE 对于小规模操作, CoreML 会增加 2-4 倍的开销 ,而在高吞吐量配置下,由于 ANE 计算时间占据主导地位,这种差距会缩小,但对于延迟敏感型工作负载(例如 LLM 令牌解码、实时推理),CoreML 的开销则非常显著。

而在这里一点,结合前面的例子,我们就可以理解,ANE 是一条极速货运流水,而 CoreML 是“标准报关”的关口,小规模操作,比如「只想寄一个小包裹」 :

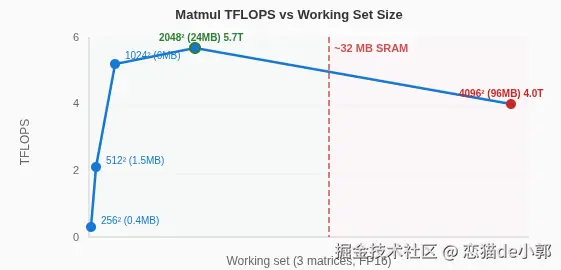

从这点看,ANE 不是通用 GPU,而是卷积优化机器 + 深流水线架构,总结下来:一个拥有 19 TFLOPS FP16 算力、32MB SRAM 缓存的“卷积加速I器”,需要通过图编译的批处理来喂饱其 16 核流水线,并具备移动端顶级的电源管理能力。

另外,M4 的 CPU 核心也采用了苹果的 SME(可扩展矩阵扩展)技术,他们之间的对比:

所以,M4 上理想的 LLM 推理策略是混合模式 :在 ANE 上进行预填充(大批量、高吞吐量),在 SME 上进行解码(单标记、对延迟敏感)。

这个就类似于:

另外,这个项目还有一些极限性能体现,例如 maderix 而为了让单步训练耗时压缩到 9.3 毫秒(持续输出 1.78 TFLOPS 的算力),必须进行极底层优化,确保 CPU 和 ANE 绝不互相等待:

cblas_sgemm) 来计算当前步的权重梯度,两者完全重叠运行。[1, C, 1, S] IOSurface 共享内存格式完全对齐。,从而消灭了数据在两个芯片间来回拷贝、转置 (Transpose) 产生的性能开销。更极客的是项目中的 exec() 重启法 ,因为 ANE 编译器存在严重的内存泄漏,在一个进程里连续编译大约 119 次后系统就会崩溃,而 每次权重更新,都必须重新编译 ANE 程序,这意味着每跑 119 步训练程序就会死掉。

而为了“逃课”,maderix 在训练循环中写了一个逻辑:定期保存当前的 Checkpoint,然后直接调用系统的 exec() 命令杀掉并重新启动自己的进程,通过这种不断“自杀并转生”的方式,暴力清空内存状态,完美绕过了苹果底层的内存泄漏限制。

基于这个,甚至有人发现 M3 Ultra 的 ANE 算力可以接近 3090 ,因为 M3 Ultra 本质上是 两个 M3 Max 级别 die 拼接(UltraFusion),两个 ANE cluster 却是可以实现真实的 37 TFLOPS :

另外,这里两个 ANE cluster 是物理分离,每个 cluster 有自己的调度,需要以双线程启动才能使用 2×ANE 。

所以整个基准测试,也可以看作是一个对 ANE 的极限性能压制场景。

github.com/maderix/ANE